[1] M. Müller, P. Dollfus and M. Schröter, "1-D Drift-Diffusion Simulation of Two-Valley Semiconductors and Devices," in IEEE Transactions on Electron Devices, vol. 68, no. 3, pp. 1221-1227, March 2021, doi: 10.1109/TED.2021.3051552.

Abstract: A two-valley formulation of 1-D drift-diffusion transport is presented that takes the coupling between the valleys into account via a new approximation for the nonlocal electric field. The proposed formulation is suitable for the simulation of III–V heterojunction bipolar transistors as opposed to formulations that employ the single electron gas approximation with a modified velocity-field model, which also causes convergence problems. Based on Boltzmann transport equation simulations, model parameters of the proposed two-valley formulation are given for GaAs, InP, InAs, and GaSb at room temperature. Applications of the new formulation are also demonstrated.

Code/Dataset: This article contains datasets made available via IEEE DataPort, a repository of datasets intended to facilitate analysis and enable reproducible research. Click the dataset name below to access it on the IEEE DataPort website.

[2] A. Rawat et al., "Experimental Validation of Process-Induced Variability Aware SPICE Simulation Platform for Sub-20 nm FinFET Technologies," in IEEE Transactions on Electron Devices, vol. 68, no. 3, pp. 976-980, March 2021, doi: 10.1109/TED.2021.3053185.

Abstract:We propose an experimentally validated physics-based process-induced variability (PIV) aware SPICE simulation framework–enabling the estimation of performance variation due to line-edge-roughness (LER), metal-gate-granularity (MGG), random-dopant-fluctuation (RDF), and oxide-thickness-variation (OTV) at sub-20 nm technology node devices. The framework utilizes LER, RDF, OTV, and MGG defining parameters such as fin-edge correlation coefficient (ρ), autocorrelation length (Λ), grain-size (GS), σ[EOT], etc. as the inputs, and produces IdVg distribution of ensemble size 250 as an output. We have validated the framework against 14 nm FinFET experimental data for IdVg trends as well as for the threshold-voltage (Vth), ON-current (Ion), and subthreshold slope (SS) distributions for a range of device dimensions with a reasonably good match. The worst and the best case R square errors are 0.64 and 0.98, respectively, for the validation. The very nature of the proposed framework allows the designers to use it for a vast range of process technologies. Such models are of dual importance, as it enables a PIV aware prediction of circuit-level performance, and provides a platform to estimate PIV parameters efficiently, on-par with sophisticated structural characterization tools.

[3] Blake W. Nelson, Andrew N. Lemmon, Sergio J. Jimenez, H. Alan Mantooth, Brian T. DeBoi, Christopher D. New, Md Maksudul Hossain, "Computational Efficiency Analysis of SiC MOSFET Models in SPICE: Dynamic Behavior," in IEEE Open Journal of Power Electronics, vol. 2, pp. 106-123, 2021, doi: 10.1109/OJPEL.2021.3056075.

Abstract: Transient simulation of complex converter topologies is a challenging problem, especially in detailed analysis tools like SPICE. Transistor models presented for SPICE are often evaluated by accuracy, with less consideration for the computational cost of model elements. In order to optimize models for application simulations, this research quantifies the relative simulation performance of modeling approaches and contextualizes the results with regard to accuracy. It is well established that the primary contributor to semiconductor dynamic behavior is the voltage-dependent interelectrode capacitances. Therefore, this study isolates these model components to resolve their influence on model accuracy and run-time. Both the voltage-dependencies modeled, and the mathematic formulation chosen strongly influence the accuracy of interelectrode capacitance models. In addition to these factors, the specific implementation chosen within SPICE also determines simulation performance. Through careful evaluation of these factors, this study offers specific recommendations for optimal implementations of interelectrode capacitances in SPICE.

Fig: DPT system schematic, components, and metrology.

[4] Sherif M. Sharroush & Yasser S. Abdalla; Parameter extraction and modelling of the MOS transistor by an equivalent resistance, Mathematical and Computer Modelling of Dynamical Systems, (2021) 27:1, 50-86, DOI: 10.1080/13873954.2020.1857790

Abstract: During the analysis of multi-transistor circuits, the need arises to evaluate the time delay or the power consumption of the circuit. Due to the complexity of the transistor model, several complicated equations arise from which a compact-form solution cannot be obtained and a suitable physical insight cannot be drawn. With this regard, two contributions are presented in this paper. The first one is a fully analytical parameter extraction approach to be applied on the MOS transistors. The second one is a quantitative method for simplifying the analysis of MOS circuits by modelling the MOS transistor by a suitable equivalent resistance adopting the time-delay or the power-consumption equivalence criteria. The parameter-extraction method is verified by using the extracted parameters in the derived expressions according to the second contribution. Compared to other representations, the agreement of the proposed model with the simulation results is very good.

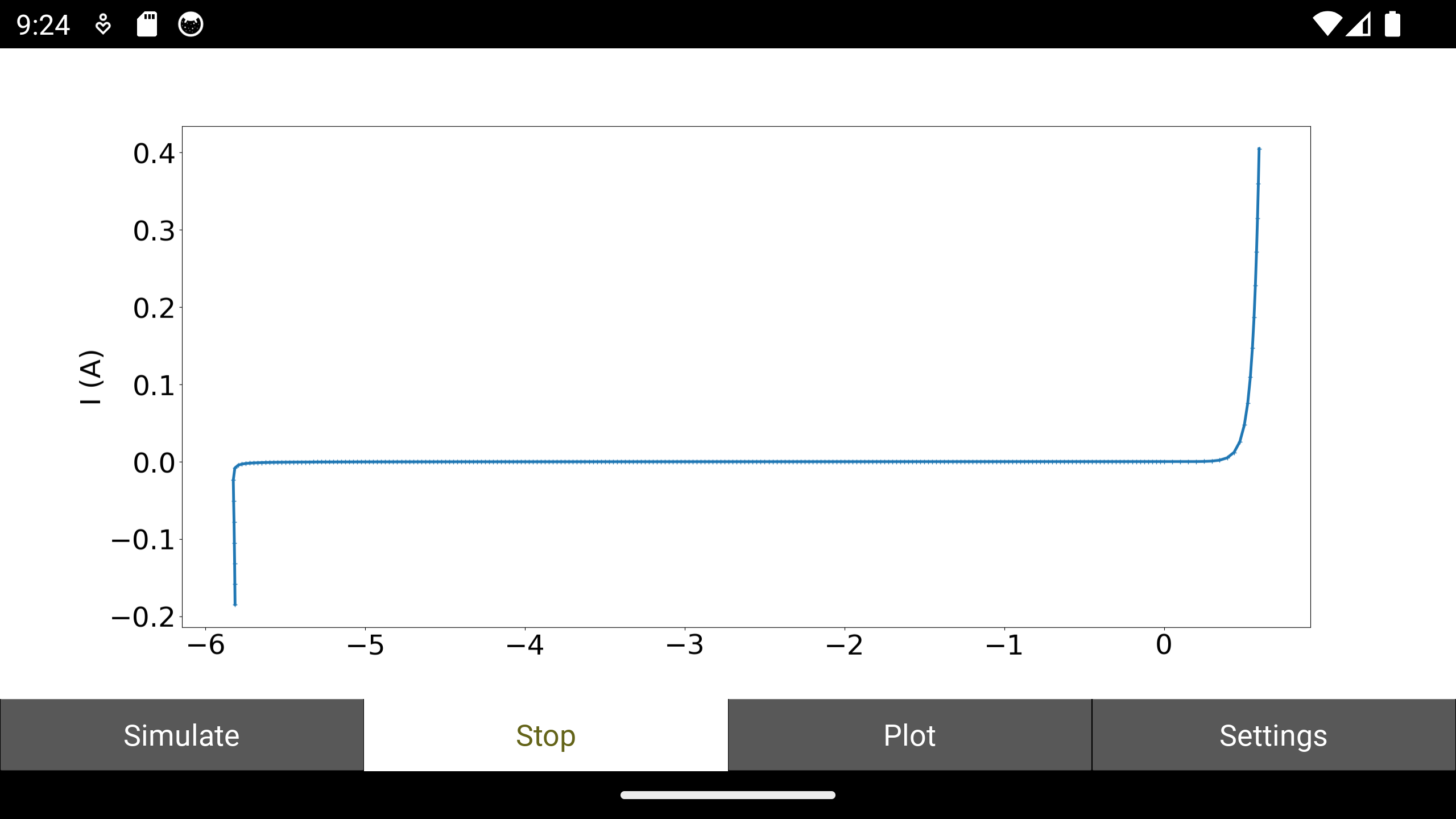

Fig: Finding Vthn0 as the intercept of the linear portion of the Id-Vgs characteristics with the horizontal axis. The curve corresponds to Vds=1V. The term ‘exact relationship’ means data from the simulation results