PSG COLLEGE OF TECHNOLOGY, COIMBATORE

9 DECEMBER, 2023

About the FreeCAD

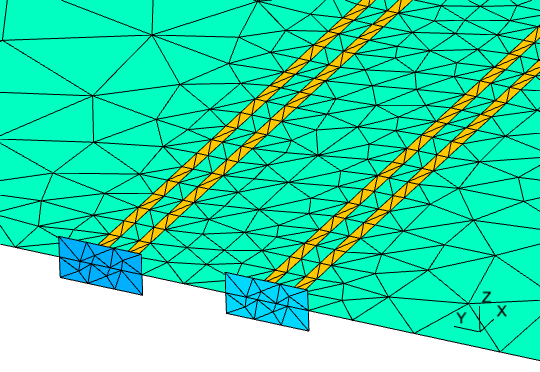

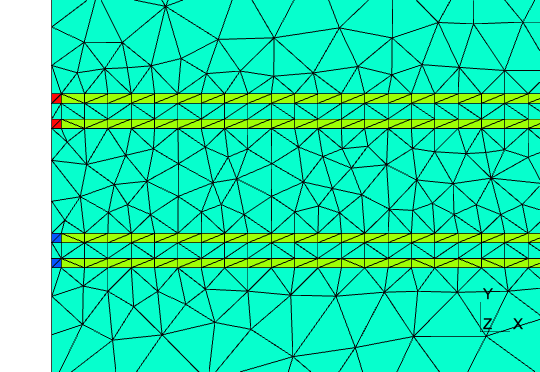

FreeCAD is a general purpose open source parametric 3D CAD modeller. FreeCAD is aimed directly at mechanical engineering and product design but, being very generic, also fits in a wider range of uses around engineering, such as architecture, finite element analysis, 3D printing, and other tasks. FreeCAD offers tools to produce, export and edit solid, full-precision models, export them for 3D printing or CNC machining, create 2D drawings and views of your models, perform analyses such as Finite Element Analyses, or export model data such as quantities or bills of materials. FreeCAD features tools similar to other popular CAD packages and therefore also falls into the category of CAD, PLM, CAx, CAE and BIM. It is a feature based parametric modeler with a modular software architecture, making it possible to provide additional functionality without modifying the core system. As with other CAD modelers, it has many 2D components in order to sketch planar shapes or create production drawings. FreeCAD is also fundamentally a social project, as it is developed and maintained by a community of developers and users united by their passion for FreeCAD. In precise FreeCAD is:

- Made to build for the real world

- A powerful solid-based geometry kernel

- A wi(l)dly parametric environment

- File formats frenzy

- A parametric constraints-based 2D sketcher

- A large (and growing) multi-specialty ecosystem

The workshop will be conducted through spoken tutorial videos of 10 minutes duration. After the workshop, a link for the video tutorials will be shared to the participants for further learning. As it is an open source software, FreeCAD can be used free of cost for educational and industrial design purposes. Participants of this workshop can install this software on their laptop during this workshop and take it with them. Target participants of this workshop include: practicing engineers, faculty members, research scholars and students.

Registration details

The registration fee for the participants (Inclusive of GST) :

- Faculty members / Students / Research Scholars : Rs. 900/-

- Industry participants : Rs.1200/-

https://forms.gle/xqcQLSTnJcYLK2DNA

Last date for registration: November 25, 2023

For any queries, contact

The Organizing Secretaries,FreeCAD Workshop, PSG College of Technology,Peelamedu, Coimbatore-641004email : vsk.amcs@psgtech.ac.in / mrp.prod@psgtech.ac.inMobile : 9952418357